# 1G Ethernet MAC Controller Core

# **Contents**

| 1  | 1G E | THERNET MAC DATA SHEET           | 1 |

|----|------|----------------------------------|---|

|    | 1.1  | FEATURES                         | 1 |

|    | 1.2  | APPLICATIONS                     | 1 |

|    | 1.3  | DELIVERABLES                     | 2 |

|    | 1.4  | LICENSING                        | 2 |

|    | 1.5  | SYMBOL                           | 3 |

|    | 1.6  | PIN DESCRIPTION                  | 3 |

|    | 1.7  | BLOCK DIAGRAM                    | 6 |

|    | 1.8  | FUNCTIONAL DESCRIPTION           | 6 |

|    | 1.9  | VERIFICATION METHODS             | 7 |

|    | 1.10 | DEVICE UTILIZATION & PERFORMANCE | 7 |

|    | 1.11 | CONTACT INFORMATION              | 7 |

|    | 1.12 | REVISION HISTORY                 | 7 |

|    |      |                                  |   |

| ln | dex  |                                  | 8 |

# **List of Figures**

| 1.1 | Symbol        | 3 |

|-----|---------------|---|

| 1.2 | Block Diagram | 6 |

# **List of Tables**

# **Chapter 1**

# **1G ETHERNET MAC DATA SHEET**

So-Logic's 10/100/1000 Mb/s Ethernet MAC core implements MAC sublayer from the IEEE Std. 802.3-2008 specification.

For the interface with the Host processor IP core uses standard AXI4-Stream interface for data transfers and AXI4-Lite interface for the configuration, and for the interface with the PCS layer standard GMII interface.

The so\_ip\_eth\_1G\_mac core can be evaluated using Xilinx Evaluation Platforms before actual purchase. This is achieved by using a demonstration bit files for KC705 platform that allows the user to connect the So-Logic's complete 1G Ethernet solution system to some other Ethernet enabled device (PC or some Ethernet tester equipment) and evaluate system performance under different transfer scenarios.

# 1.1 FEATURES

- Fully compliant with the IEEE Std. 802.3-2008 specification

- · Configurable half-duplex and fullduplex operation

- Supports 10/100/1000 Mb/s Ethernet communication speeds

- · AXI4-Stream user side interface for transmission and reception of Ethernet frames

- · Supports GMII as well as providing connectivity to So-Logic's 1000Base-X PCS core

- · Low frequency operation

- IP Core system clocks at 125 MHz for 10/100/1000 Mb/s data rates

- · Configuration and monitoring through an AXI4-Lite interface

- · MAC flow control pause frame support

- · Statistic counters

- · Configurable interframe gap

- · Automatic padding and FCS calculation

- · Configurable support for the jumbo frames

- · Configurable maximum frame length check

- · Configurable receive address filter

# 1.2 APPLICATIONS

- · LAN networking

- Industrial Ethernet

- · Distributed Storage Area Networks

- · Cloud computing

# 1.3 DELIVERABLES

- · Source code:

- VHDL Source Code

- · VHDL test bench environment

- Tests with reference responses

- · Technical documentation

- Datasheet

- Installation notes

- User manual

- · Instantiation templates

- · Example application

- · Technical Support

- IP Core implementation support

- Variable length maintenance

- Delivery of IP Core updates, minor and major changes

- Delivery of documentation updates

- Telephone & email support

# 1.4 LICENSING

## **Netlist License**

- · Post-synthesis netlist

- · Self checking testbench

- · Test vectors for testing the core

- · Place&Route scripts

- Constraints

- · Instantiation template

- Documentation

# **VHDL Source License**

- · VHDL RTL source code

- Complete verification plan together with the functional verification environment to verify the correct operation of the core

- · Self checking test bench

- · Vectors for testing the functionality of the core

- · Simulation & synthesis scripts

- Documentation

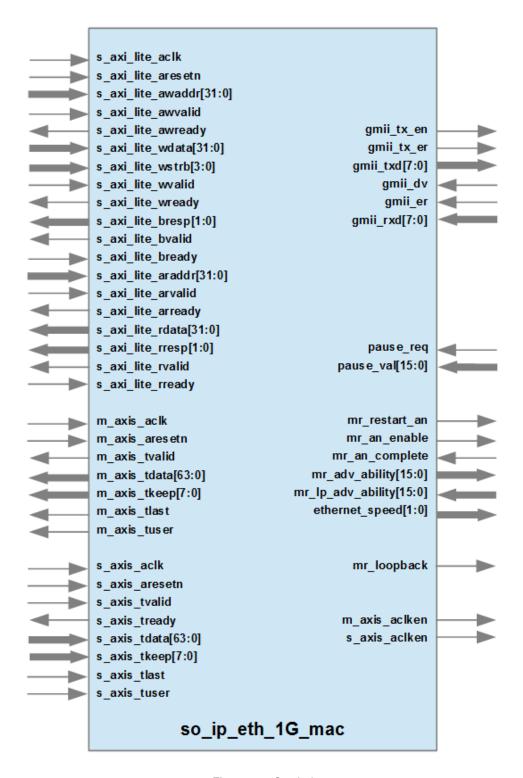

# 1.5 SYMBOL

Figure 1.1: Symbol

# 1.6 PIN DESCRIPTION

| Name | Signal Direction | Description |

|------|------------------|-------------|

3

| AXI4 Lite Interface                          |        |                                                              |

|----------------------------------------------|--------|--------------------------------------------------------------|

| s_axi_lite_aclk                              | Input  | Clock for AXI4-Lite                                          |

| s_axi_lite_aresetn                           | Input  | Local reset for AXI4-Lite interface                          |

| s_axi_lite_awaddr[31:0]                      | Input  | Write Address                                                |

| s_axi_lite_awvalid                           | Input  | Write Address valid                                          |

| s_axi_lite_awready                           | Output | Write Address ready                                          |

| s_axi_lite_wdata[31:0]                       | Input  | Write Data                                                   |

| s_axi_lite_wstrb[3:0]                        | Input  | Unused                                                       |

| s_axi_lite_wvalid                            | Input  | Write Data valid                                             |

| s_axi_lite_wready                            | Output | Write Data ready                                             |

| s_axi_lite_bresp[1:0]                        | Output | Write Response                                               |

| s axi lite bvalid                            | Output | Write Response valid                                         |

| s_axi_lite_bready                            | Input  | Write Response ready                                         |

| s_axi_lite_araddr[31:0]                      | Input  | Read Address                                                 |

| s_axi_lite_arvalid                           | Input  | Read Address valid                                           |

| s_axi_lite_arready                           | Output | Read Address ready                                           |

| s_axi_lite_arready<br>s_axi_lite_rdata[31:0] | -      | Read Data                                                    |

|                                              | Output |                                                              |

| s_axi_lite_rresp[1:0]                        | Output | Read Response                                                |

| s_axi_lite_rvalid                            | Output | Read Data/Response valid                                     |

| s_axi_lite_rready                            | Input  | Read Data/Response ready                                     |

| AXI4 Stream Receive Interface                |        | OL LI LIAVIA D                                               |

| m_axis_aclk                                  | Input  | Clock to which all AXI4 Receive                              |

|                                              |        | signals are synchronous                                      |

| m_axis_aresetn                               | Input  | AXI4 Stream reset signal                                     |

| m_axis_tvalid                                | Output | Indicates that m_axis_tdata                                  |

|                                              |        | contains valid frame data                                    |

| m_axis_tdata[63:0]                           | Output | Frame data, split into 8 lanes                               |

| m_axis_tkeep[7:0]                            | Output | Indicate which lanes of the                                  |

|                                              |        | m_axis_tdata are carrying valid                              |

|                                              |        | data. Other lanes should be ignored                          |

| m_axis_tlast                                 | Output | Indicates that the last 64b word of                          |

|                                              |        | frame data is sent to the user                               |

| m_axis_tuser                                 | Output | When asserted together with                                  |

|                                              |        | m_axis_tlast, this signal indicates                          |

|                                              |        | that the received frame should be                            |

|                                              |        | ignored because it has been                                  |

|                                              |        | identified that it contains errors                           |

| AXI4 Stream Transmit Interface               |        |                                                              |

| s_axis_aclk                                  | Input  | Clock to which all AXI4 Transmit                             |

|                                              |        | signals are synchronous                                      |

| s_axis_aresetn                               | Input  | AXI4 Stream reset signal                                     |

| s_axis_tvalid                                | Input  | Indicates that s_axis_tdata contain                          |

| <del>_</del>                                 |        | valid frame data. Should be at '1' all                       |

|                                              |        | the time during the frame                                    |

|                                              |        | transmission.                                                |

| s_axis_tready                                | Output | Indicates that the core has read                             |

|                                              |        | current data and that new data need                          |

|                                              |        | to be supplied                                               |

| 1                                            | Input  | Frame data, split into 8 lanes                               |

| s axis tdatal63:01                           |        | i i i i i i i i i i i i i i i i i i i                        |

|                                              |        |                                                              |

| s_axis_tdata[63:0]<br>s_axis_tkeep[7:0]      | Input  | Indicate which lanes of the s_axis_tdata contain valid data. |

| s_axis_tlast               | Input   | Indicates that the last 64b word of      |

|----------------------------|---------|------------------------------------------|

|                            |         | data is transmit to the core             |

| s_axis_tuser               | Input   | When asserted during frame               |

|                            |         | transmission user indicates that the     |

|                            |         | frame should be dropped (the core        |

|                            |         | will flag that the frame contains error) |

| GMII Interface             |         |                                          |

| gmii_tx_en                 | Output  | GMII transmit enable output signal       |

| gmii_tx_er                 | Output  | GMII transmit error output signal        |

| gmii_txd[7:0]              | Output  | GMII transmit data output signal         |

| gmii_dv                    | Input   | GMII receive data valid input signal     |

| gmii_er                    | Input   | GMII receive error input signal          |

| gmii_rxd[7:0]              | Input   | GMII receive data input signal           |

| Pause Interface            |         |                                          |

| pause_req                  | Input   | Pause request input port                 |

| pause_val[15:0]            | Input   | Duration of the requested pause,         |

|                            |         | measured in time quanta that last for    |

|                            |         | 512 bits                                 |

| Auto-Negotiation Interface |         |                                          |

| mr loopback                | Output  | Operate PCS in loopback mode             |

| mr_restart_an              | Output  | Restarts the Auto-Negotiation            |

|                            |         | process                                  |

| mr an enable               | Output  | When high enables the                    |

|                            |         | auto-negotiation process                 |

| mr_an_complete             | Input   | Signals that auto-negotiation has        |

| '                          | '       | completed successfully                   |

| mr_adv_ability[15:0]       | Output  | For SGMII auto-negotiation               |

|                            |         | advertisement ability is hardwired to    |

|                            |         | the value 0x4001                         |

| mr_lp_adv_ability[15:0]    | Input   | Holds the link partner ability after     |

| _h %t1                     |         | auto-negotiation has completed           |

| ethernet_speed[1:0]        | Input   | Indicates which speed should be          |

|                            |         | used for MAC clocking: 00 – 10Mbps       |

|                            |         | (1.25MHz), 01 – 100Mbps                  |

|                            |         | (12.5MHz), 10 – 1Gbps (125MHz),          |

|                            |         | 11 - reserved                            |

| m axis aclken              | Output  | Clock-Enable signals for AXI RX and      |

| m_axis_acincm              | Cutput  | TX user logic. These output signals      |

|                            |         | generate the correct clock-enable        |

|                            |         | pulses for the RX and TX logic           |

|                            |         | connected to the 1G MAC Controller       |

|                            |         |                                          |

|                            |         | core when operating with 100M and        |

| a avia callean             | Outrout | 10M links                                |

| s_axis_aclken              | Output  | Holds the link partner ability after     |

|                            |         | auto-negotiation has completed           |

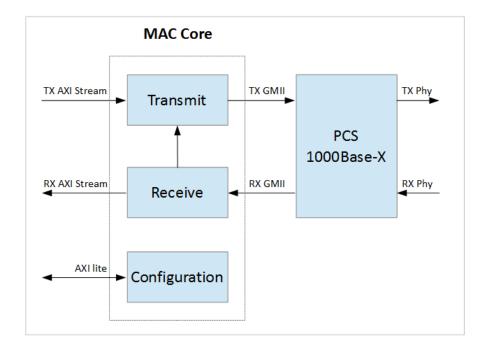

# 1.7 BLOCK DIAGRAM

Figure 1.2: Block Diagram

# 1.8 FUNCTIONAL DESCRIPTION

The previous diagram shows all major modules of the so\_ip\_eth\_1G\_mac core that is described here in more detail.

## **MAC Receive**

10/100/1000 Mb/s Ethernet MAC Controller MAC Receive is responsible for the frame reception which includes:

- 1. Frame boundary recognition

- 2. Recognition of collision fragments

- 3. Address recognition and frame filtering

- 4. Error checking

- 5. Frame disassembly

- 6. User data output using AXI4 8b Stream protocol

- 7. Tracking statistics

## **MAC Transmit**

10/100/1000 Mb/s Ethernet Controller MAC Transmit module takes a user supplied frame from the AXI bus and transmits the data to the GMII output. 10/100/1000 Mb/s Ethernet MAC Controller MAC Transmit includes following responsibilities:

- 1. Add the preamble to the user frame

- 2. Add SFD (Start Frame Delimiter) to the user frame

- 3. Add FCS to the user frame

- 4. Check the length of the input frame

- 5. Makes an inter-frame gap between frames

#### 1.9 VERIFICATION METHODS

- 6. Track statistic of the transmitted frames

- 7. In half-duplex mode implements CSMA/CD doctrine

#### Flow Control

10/100/1000 Mb/s Ethernet Flow Control has two functions:

- 1. Generates pause frames from a dedicated interface

- 2. Recognizes the pause frames and responds to them

# 1.9 VERIFICATION METHODS

10/100/1000 Mb/s Ethernet MAC controller core was tested both using sophisticated verification environment and in dedicated hardware platform. Verification environment, together with the developed verification plan, was used to extensively verify the 10/100/1000 Mb/s Ethernet MAC controller core operation is in accordance with the IEEE Std. 802.3-2008 specification. After reaching all verification goals, IP core was tested using dedicated hardware platforms, namely Xilinx's KC-705 Evaluation Platform. Using these platforms 10/100/1000 Mb/s Ethernet MAC controller core was implemented in FPGA and connected to various Ethernet-enabled devices to test its operation in a real application and to estimate the performance of the core. The details about the verification methodology that was used and performance results during hardware testing can be obtained from So-Logic upon request.

# 1.10 DEVICE UTILIZATION & PERFORMANCE

| Supported | Device         | Slices | Slice LUTs | Slice FFs | IOs | BRAMs | MGTs |

|-----------|----------------|--------|------------|-----------|-----|-------|------|

| Family    |                |        |            |           |     |       |      |

| Kintex-7  | XC7K325T-<br>2 | 1785   | 3326       | 4009      | 379 | 0     | 0    |

| Zynq      | XC7Z045-2      | 1785   | 3326       | 4009      | 379 | 0     | 0    |

### Notes:

- 1. All core I/O signals are routed off chip

- 2. Results were obtained using Xilinx Vivado Design Suite 2014.3 software

- 3. The synthesis results provided are for reference only. Please contact So-Logic for estimates for your particular application.

# 1.11 CONTACT INFORMATION

So-Logic

Lustkandlgasse 52/22

A-1090 Vienna

Austria/Europe

Phone: +43-1-3157777-11 Fax: +43-1-3157777-44

E-Mail: ip\_ethernet@so-logic.net

URL: http://www.so-logic.net

# 1.12 REVISION HISTORY

The following table shows the revision history for this document.

# **1G ETHERNET MAC DATA SHEET**

| Date     | Version | Revision         |

|----------|---------|------------------|

| 01/11/14 | 1.0     | Initial release. |